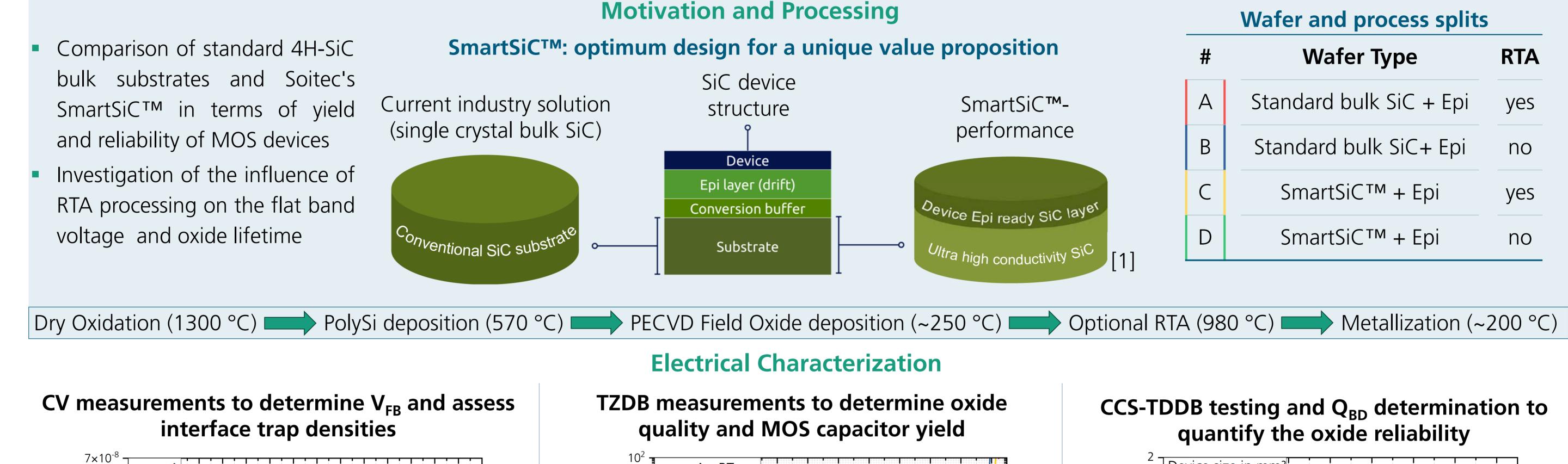

Gate Oxide Performance and Reliability on SmartSiC<sup>™</sup> Wafers and the Influence of RTA processing on Gate Oxide Lifetime

## <u>Tom Becker<sup>1</sup></u>, Mathias Rommel<sup>1</sup>, Holger Schlichting<sup>1</sup>, Leander Baier<sup>1</sup>, Eric Guiot<sup>2</sup>, Frédéric Allibert<sup>2</sup>

tom.becker@iisb.fraunhofer.de

<sup>1</sup> Fraunhofer IISB, Schottkystr. 10, 91058 Erlangen, Germany <sup>2</sup> Soitec, Parc Technologique des Fontaines, 38190 Bernin, France

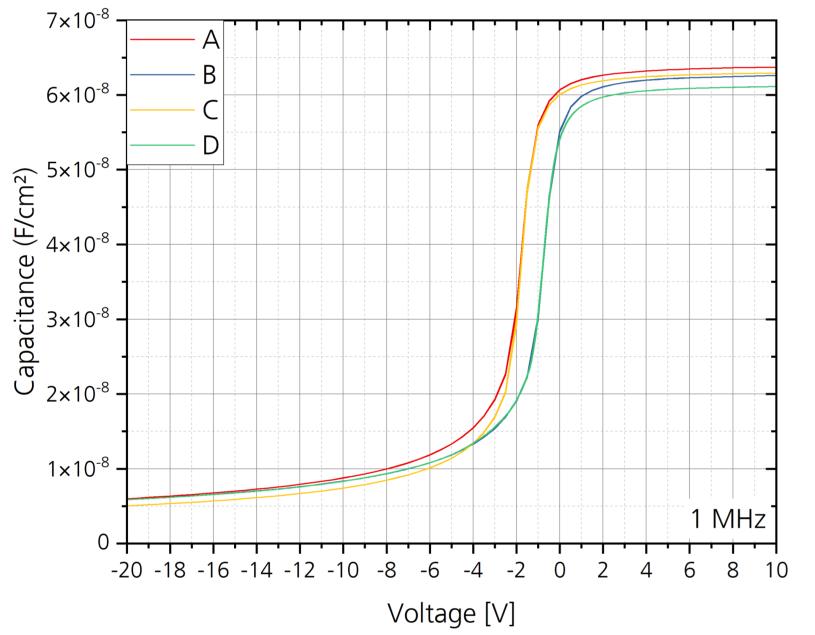

- No distinction between Bulk SiC and SmartSiC<sup>™</sup>

- $\sim$  > 1 V shift of V<sub>FB</sub>, assumed partially due to incomplete dopant activation in the polysilicon gate electrode [2] in the absence of RTA

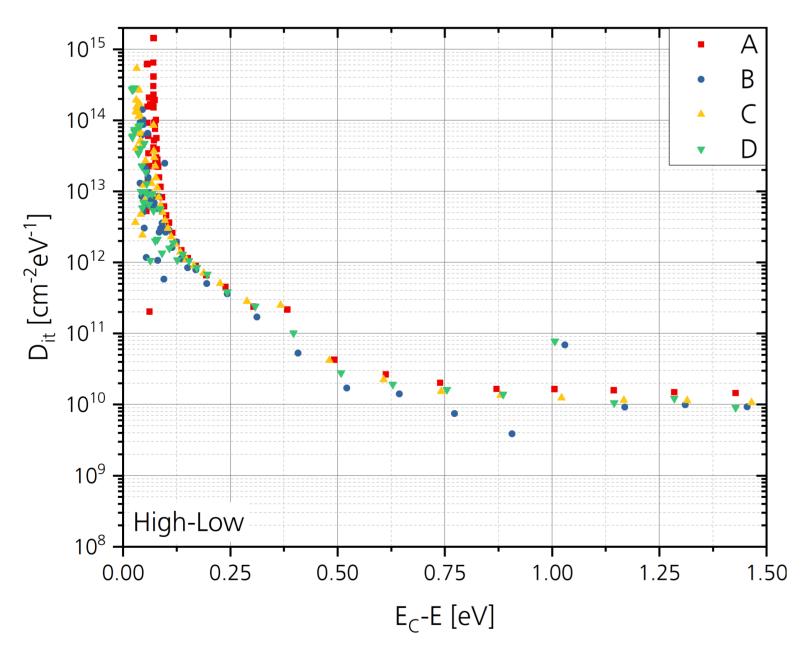

D<sub>it</sub> characteristics from High-Low and Terman paper) methods show no significant (see

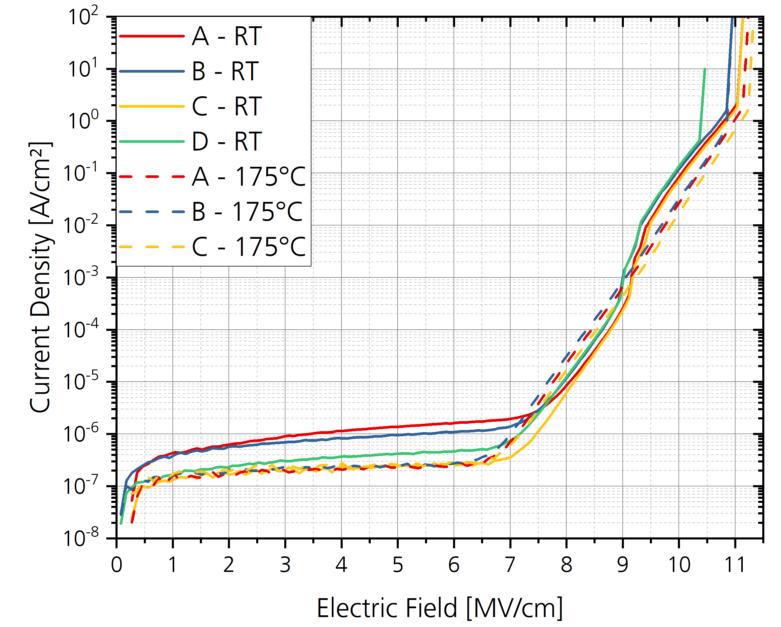

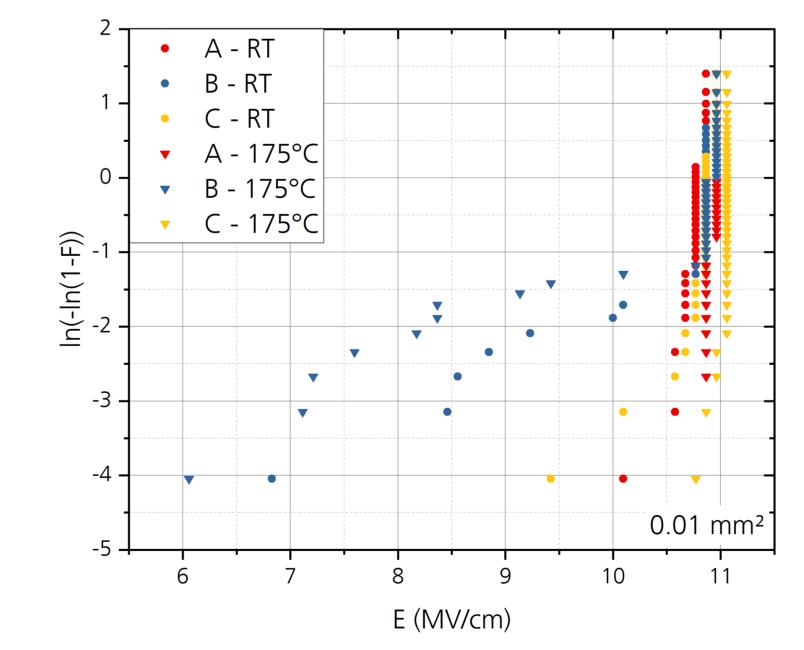

Breakdown behavior of all samples overlap independent of measurement temperature, electric field calculated with consideration of different V<sub>FR</sub> values

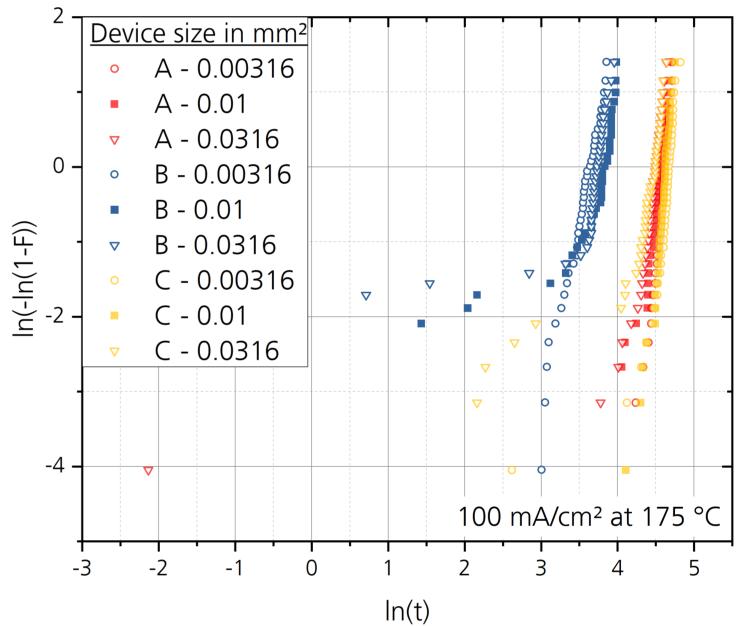

Yield analysis for all sizes and temperatures display no notable differences between standard Weibull plots of TDDB investigations at different temperatures and device sizes show a clear gap in oxide lifetime between RTA and non-RTA processed wafers

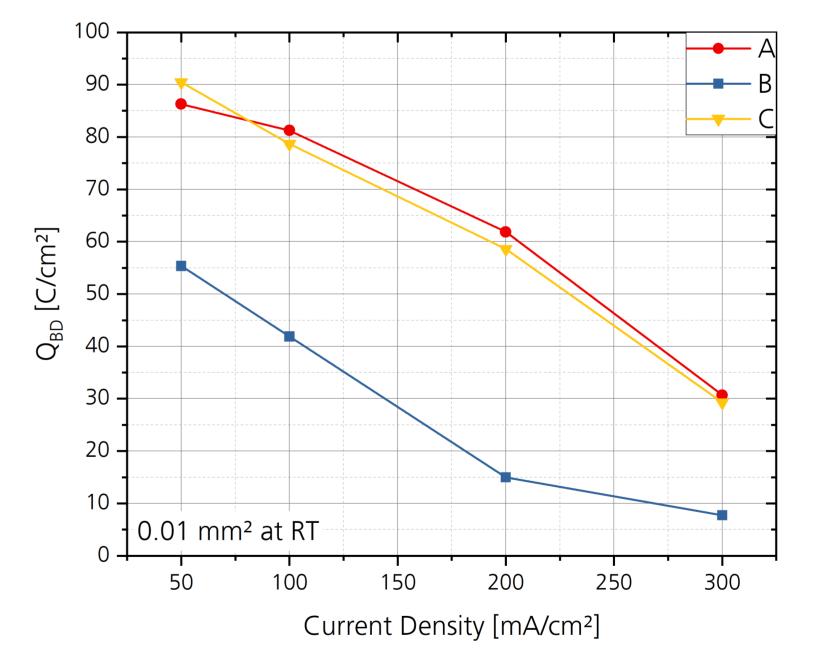

Both CCS-TDDB and Q<sub>BD</sub> extraction at a failure rate of 63 % show identical oxide reliability

## distinction between all samples

bulk substrates and SmartSiC<sup>™</sup> material

Non-RTA samples demonstrate more early failures

behavior for SmartSiC<sup>™</sup> and standard bulk wafers

## Conclusion

- After extensive analysis of MOS capacitors on both SmartSiC<sup>™</sup> and standard bulk 4H-SiC wafers, no measurable differences were discovered.

- Skipping the RTA step induces a > 1 V shift in the V<sub>FB</sub> and degrades the oxide reliability (over 30 % reduction in TDDB and Q<sub>BD</sub>). The origin was suggested to be partially caused by incomplete activation of the phosphorous doped polysilicon gate electrode. Other possible contributions are still under investigation.

- N. Daval et al., 6th IEEE Electron Devices Technology & Manufacturing Conference, pp. 85-87, 2022

- 2 S. Kallel, Materials Science in Semiconductor Processing, Volume 1, Issues 3–4, p. 299-302 (1998)

## TRANSFORM

This work is supported by the H2020 - ECSEL JU programme of the European Union under the grant of the TRANSFORM project 'Trusted European SiC Value Chain for a greener Economy' (ECSEL JU Grant No. 101007237).